#### Data Acquisition System

Prof. Dr. M. Zahurul Haq zahurul@me.buet.ac.bd http://teacher.buet.ac.bd/zahurul/

Department of Mechanical Engineering Bangladesh University of Engineering & Technology

ME 361: Instrumentation & Measurement

Prof. Dr. M. Zahurul Haq (BUET)

ME 361

#### Digital to Analog Conversion (DAC)

- A DAC converts a digital 'word' consisting of a number of bits into a voltage or current that represents the binary number value of the digital word.

- An 8-bit DAC, for example, may produce an output signal of 0 V when the binary word applied to its digital input is  $00000000_2$ , and 2.55 V when the digital inputs see a word of 111111111<sub>2</sub>.

- Similar to analog input configuration, a common DAC is shared among multiplexed output signals.

- Standard analog output ranges are essentially same as analog inputs:  $\pm 5$  V dc,  $\pm 10$  V dc, 0 - 10 V dc, and 4-20 mA dc.

DAS Prof. Dr. M. Zahurul Haq (BUET) ME 361 Digital to Analog Conversion (DAC)

### Digital to Analog Conversion

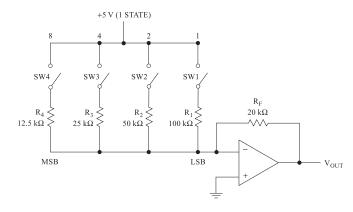

DACs or D/A converters are used to convert digital signals representing binary numbers into proportional analog voltages.

e566.eps

A 4-bit input Binary-weighted D/A converter

Prof. Dr. M. Zahurul Haq (BUET)

ME 361

Digital to Analog Conversion (DAC)

$$I=E_{ref}\sum_{M=1}^{N}rac{c_m}{2^{m-1}R}$$

$$E_o = IR_r$$

$C_m = 0 \ or \ 1$ : depending on the mth bit value of the register that controls the switch setting.

Prof. Dr. M. Zahurul Haq (BUET)

e570.eps

DAS

ME 361

Digital to Analog Conversion (DAC)

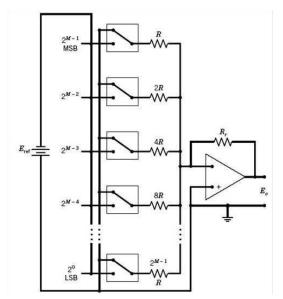

- The binary weighted resistor ladder suffers from a series drawback in actual practice. The values of input resistors tend to become very large and very small at the ends of the range as the bit length of the input word becomes larger.

- If R is set to 10 k $\Omega$ , then  $R_8$  will be 1.28 M $\Omega$ . If we assume a reference potential E of 5.0 V, then  $I_8$  will be only 3.9  $\mu$ A which is too small to be resolved because of the noise problems.

- In commercial DACs, all the resistors have a value of either R or 2R. The gain of the amplifier is unity, so  $E_o$  can be expressed as:

$$E_o = E \sum_{i=1}^n rac{a_i}{2^i}$$

(provided that  $R_L >> R$ , so that the voltage divider effect between the ladder and  $R_L$  can be safely neglected).

Prof. Dr. M. Zahurul Haq (BUET)

DAS

ME 361

5 / 23

Analog to Digital Converter (ADC)

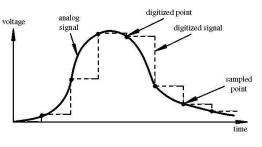

# A/D Conversion Compromises

e054.eps

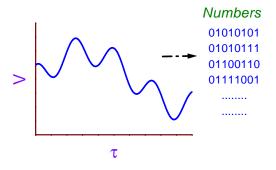

A/D conversion processes pose two primary challenges:

- Quantization refers to uncertainty introduced upon conversion of an analog voltage to a digital number.

- ② Sampling refers to acquiring data only at discrete intervals, with no informations in between.

Analog to Digital Converter (ADC)

### Analog to Digital Conversion

- In A/D conversion process continuous electrical signals are converted to the digital language of computers.

- If a 8-bit ADC has a 0-to-2.55 V input signal range, then a 0 V input could produce an output word of 000000002, while the +2.55 V level seen at the input would produce an output word of 1111111112.

e048.eps

Prof. Dr. M. Zahurul Haq (BUET)

DAS

ME 361 6 / 2

Analog to Digital Converter (ADC)

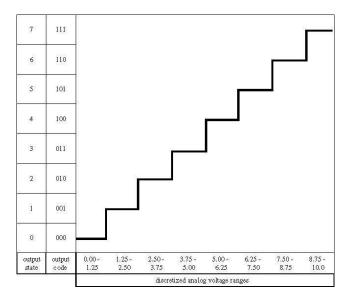

# Analog to Digital Conversion

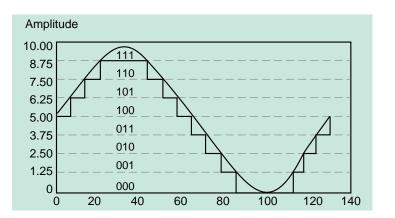

e055.eps

Digitized Sine Wave with a Hypothetical 3-Bit ADC

Analog to Digital Converter (ADC)

e573.eps

Prof. Dr. M. Zahurul Haq (BUET)

DAS

ME 361

Analog to Digital Converter (ADC)

# Range of Values of Digital Quantities

| No of bits | Number of States   | Resolution (%) |  |

|------------|--------------------|----------------|--|

| 1          | $2^1 = 2$          | 50             |  |

| 2          | $2^2 = 4$          | 25             |  |

| 3          | $2^3 = 8$          | 12.5           |  |

| 4          | $2^4 = 16$         | 6.25           |  |

| 8          | $2^8 = 256$        | 0.391          |  |

| 10         | $2^{10} = 1024$    | 0.098          |  |

| 12         | $2^{12} = 4096$    | 0.024          |  |

| 16         | $2^{16} = 65536$   | 0.001526       |  |

| 20         | $2^{20} = 1048576$ | 0.000095       |  |

11 / 22

Analog to Digital Converter (ADC)

#### Resolution & Quantization

• Resolution refers to the smallest signal that can be detected by a measurement system. It can be expressed in bits, in proportions, on in percentage of full scale.

$$Resolution \equiv Q = rac{E_{

m Full~Scale}}{2^{

m Number~of~Bits}}$$

- A system may have 12-bit resolution, one part in 4096 resolution, and 0.0244% of full scale.

- Quantization error is the inherent uncertainty in an A/D conversion due to the finite resolution of the system.

- $\bullet$  An 8-bit ADC with  $E_{FS}$  of 10 V could detect a minimum of 10/256 = 0.0391 V. The higher the resolution, the smaller the detectable voltage change.

- How many bits are needed to obtain a resolution of 0.01%?

Prof. Dr. M. Zahurul Haq (BUET)

DAS

ME 361

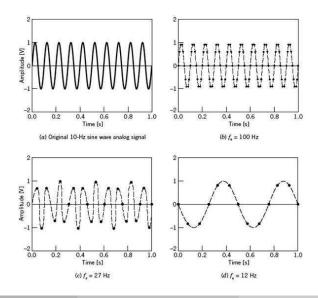

Analog to Digital Converter (ADC) Sampling

# Analog Signal & Sampled Equivalent

e571.eps

DAS

e572.eps

Analog to Digital Converter (ADC) Sampling

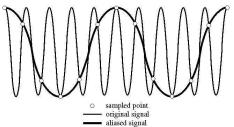

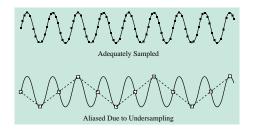

# Shanon's Sampling Theorem

To faithfully represent the analog signal, sampling frequency  $f_s$  such that must be greater than Nyquist frequency,  $f_N$ :

$$f_s > f_N \equiv 2f_{max}$$

- Time interval between the digital samples is  $\Delta t = 1/f_s$

- If  $f_s < f_N$ , aliasing can result and totally non-existent frequencies may be indicated.

e056.eps

Prof. Dr. M. Zahurul Haq (BUET)

DAS

ME 361

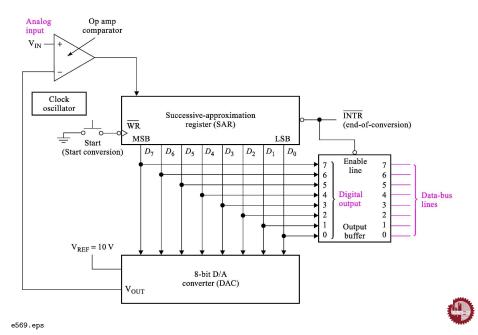

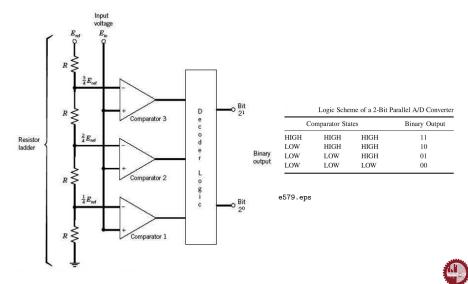

Analog to Digital Converter (ADC) ADC Hardware

# Types of A/D Converters

- Successive Approximation (SA) ADC

- ② Flash/Parallel ADC

- 3 Dual-slope Integrating ADC

- 4 Servo/Binary-counter/Ramp ADC

| Туре | Speed  | Resolution | Noise Immunity | Cost   |

|------|--------|------------|----------------|--------|

| 1.   | Medium | 10-16 bits | Poor           | Low    |

| 2.   | Fast   | 4-8 bits   | None           | High   |

| 3.   | Slow   | 12-18 bits | Good           | Low    |

| 4.   | Slow   | 14-24 bits | Good           | Medium |

Analog to Digital Converter (ADC) Sampling

#### Example: Effect of Sampling Rate

e574.eps

Prof. Dr. M. Zahurul Haq (BUET)

DAS

ME 361

Analog to Digital Converter (ADC) ADC Hardware

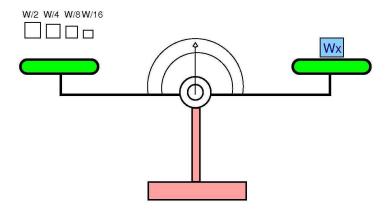

# Successive Approximation ADC

SA ADC is like a platform balance

Measurement is possible if unknown wt. Wx <W

DAS

Prof. Dr. M. Zahurul Haq (BUET) DAS ME 361

Analog to Digital Converter (ADC) ADC Hardware

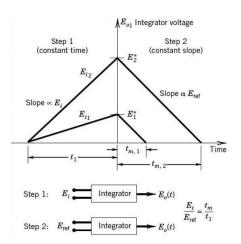

### Dual-slope Integrating ADC

e568.eps

Output represents the integral or average of an input voltage over a a fixed period of time. Hence, it smooths out signal noise.

19 / 22

- A SA register(SAR) contains the control logic, a shift register, and a set of output latches, one for each register section. The outputs of the latches drive a DAC.

- A start pulse sets D7 (first bit of the shift register, MSB) high. DAC sees the word 10000000<sub>2</sub> & generates the output voltage,  $V_{out}=1/2E_{FS}.$  If  $V_{IN}>V_{out},$  then the D7 latch is set high, else it is set low.

- On the next clock pulse, D6 latch is set high. The process is continued through to LSB. If, on any trial, it is found that  $V_{IN} < V_{out}$ , then the corresponding bit is reset low. The process is continued until the voltages match within the least significant bit.

Prof. Dr. M. Zahurul Haq (BUET)

DAS

ME 361

Analog to Digital Converter (ADC) ADC Hardware

#### Parallel or Flash ADC

e578.eps

Prof. Dr. M. Zahurul Haq (BUET)

DAS

ME 361

Analog to Digital Converter (ADC) ADC Hardware

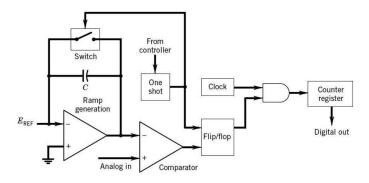

#### Ramp ADC

e577.eps

$E_{ref}$ , initially at zero, is increased at a set time steps & the ramp level is compared with the input voltage. The comparison is continued until the two are equal. The comparator output then goes to zero. It flips a flip-flop and the register count value will then indicate the digital binary equivalent of the input voltage.

Prof. Dr. M. Zahurul Haq (BUET) ME 361 21 / 22 Analog to Digital Converter (ADC) ADC Hardware

# **ADC Speed Parameters**

- 1 Acquisition: is the time required by the front-end analog circuitry to acquire a signal. Also called aperture time, it is the time for which the converter must see the analog voltage in order to complete a conversion.

- 2 Conversion: is the time needed to produce a digital value corresponding to the analog value.

- 3 Transfer: is the time needed to send the digital value to the host computer's memory.

Throughput, then, equals the number of channels being served divided by the time required to do all three functions.

ME 361

Prof. Dr. M. Zahurul Haq (BUET) DAS